Phase Lock Loop System Design Theory and Principles RAHRF469

- 24.06.2021

- 236

MP4 | Video: h264, 1280x720 | Audio: AAC, 48000 Hz

Language: English | Size: 1.73 GB | Duration: 6h 10m

Language: English | Size: 1.73 GB | Duration: 6h 10m

What you'll learn

A complete system overview of Phase Lock Loop Topic

Requirements

RAHRF152 Modulation for Communication systems

RAHRF101 RF Basic Concepts and Components

Circuit theory

or have taken similar courses on the topics above

Description

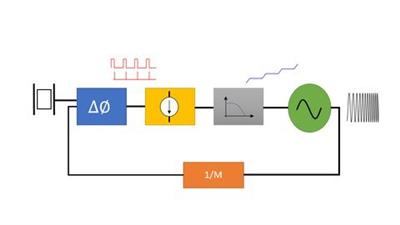

This course focuses on phase locked loops (PLL) theory and behavioral modeling. PLLs are one of the most important blocks in RF communication transceiver systems. PLL systems exist in variety of high frequency applications, from simple clock circuits, to local oscillators (LOs) for high performance radio communication links, and ultra-fast switching frequency synthesizers in vector network analyzers (VNA). This course explains different types of PLLs with detailed explanations on individual sub-blocks. It includes PLL design and calculations with lots of examples and homework. There are also system level simulations and behavioral design using Advanced Design System (ADS) software. Phase noise of PLL is discussed in this course using equations, systems analysis, and there are tutorials that guide you to simulate the behavioral phase noise model of PLL and observe the system impact on VCO phase noise. There are also discussion about fractional PLL concept and features in this course.

It is important to remind you that this course covers the behavioral analysis of PLL sub-blocks however, it does not include any transistor level simulation and this topic will be covered on different course which will be released by Rahsoft in the future.

Prerequisites and topics you need to be familiar with for this course are:

Electronics and analog circuit design (intermediate level)

Control Theory (basic level)

ADS software

Concepts such as:

open and closed Loop gain

Open loop - close loop systems

Feedback

Transfer function

Phase margin

CMOS transistor

Basic op amp

Laplace transform

Please be advised that this course contains more math than previous courses.

PLL system design requires an understanding of transfer function derivations and stability analysis which needs system calculations and involves university level mathematical calculations.

Who this course is for:

Electrical Engineers

Communication Engineers

RF Engineers

Communication Enthusiasts

Screenshots

Download link:

rapidgator_net:

https://rapidgator.net/file/6fcb53c0e5420a8d4bc428eae6c5026e/0hmyi.Phase.Lock.Loop.System.Design.Theory.and.Principles.RAHRF469.part1.rar.html

https://rapidgator.net/file/037eff350fdaa605b03ae10fb0a638ba/0hmyi.Phase.Lock.Loop.System.Design.Theory.and.Principles.RAHRF469.part2.rar.html

uploadgig_com:

https://uploadgig.com/file/download/ee37599467328FA9/0hmyi.Phase.Lock.Loop.System.Design.Theory.and.Principles.RAHRF469.part1.rar

https://uploadgig.com/file/download/7096FbaF6d9940Dc/0hmyi.Phase.Lock.Loop.System.Design.Theory.and.Principles.RAHRF469.part2.rar

nitroflare_com:

https://nitro.download/view/762A8C411683BE6/0hmyi.Phase.Lock.Loop.System.Design.Theory.and.Principles.RAHRF469.part1.rar

https://nitro.download/view/2C8175129F86359/0hmyi.Phase.Lock.Loop.System.Design.Theory.and.Principles.RAHRF469.part2.rar

https://rapidgator.net/file/6fcb53c0e5420a8d4bc428eae6c5026e/0hmyi.Phase.Lock.Loop.System.Design.Theory.and.Principles.RAHRF469.part1.rar.html

https://rapidgator.net/file/037eff350fdaa605b03ae10fb0a638ba/0hmyi.Phase.Lock.Loop.System.Design.Theory.and.Principles.RAHRF469.part2.rar.html

uploadgig_com:

https://uploadgig.com/file/download/ee37599467328FA9/0hmyi.Phase.Lock.Loop.System.Design.Theory.and.Principles.RAHRF469.part1.rar

https://uploadgig.com/file/download/7096FbaF6d9940Dc/0hmyi.Phase.Lock.Loop.System.Design.Theory.and.Principles.RAHRF469.part2.rar

nitroflare_com:

https://nitro.download/view/762A8C411683BE6/0hmyi.Phase.Lock.Loop.System.Design.Theory.and.Principles.RAHRF469.part1.rar

https://nitro.download/view/2C8175129F86359/0hmyi.Phase.Lock.Loop.System.Design.Theory.and.Principles.RAHRF469.part2.rar

Links are Interchangeable - No Password - Single Extraction